在電子工程領域,尤其是涉及高速、高密度電路的設計中,電磁兼容性(EMC)已成為衡量產品可靠性的核心指標。業內常言“90%的EMC問題是設計出來的”,這句話深刻地揭示了EMC問題的根源——它們并非偶然產生,而是在設計階段就埋下了伏筆。這一論斷在集成電路(IC)設計中體現得尤為明顯和關鍵。

我們需要理解EMC的本質。EMC是指設備或系統在其電磁環境中能正常工作,且不對該環境中的任何其他設備構成無法承受的電磁干擾的能力。它包含兩個方面:電磁干擾(EMI)和電磁抗擾度(EMS)。一旦芯片設計完成并流片生產,其物理結構、布線、電源分布、信號完整性等特性便已固化。后期通過外部屏蔽、濾波或布局調整來“修補”EMC問題,往往成本高昂、效果有限,且可能影響性能。因此,將EMC考量前置到芯片設計階段,是最高效、最經濟的策略。

具體到集成電路設計,以下幾個關鍵環節直接決定了最終的EMC表現,也恰恰是“設計出來”的根源所在:

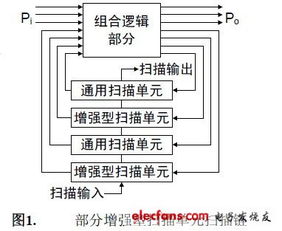

- 架構與電源規劃:芯片的頂層架構和電源分配網絡(PDN)設計是EMC的基石。糟糕的電源規劃會導致嚴重的電源噪聲(如地彈、電源軌道塌陷),這些噪聲會通過電源引腳輻射出去或耦合到信號中,成為主要的干擾源。設計階段對電源域劃分、去耦電容的布置、電源網格阻抗的控制,直接決定了電源的純凈度。

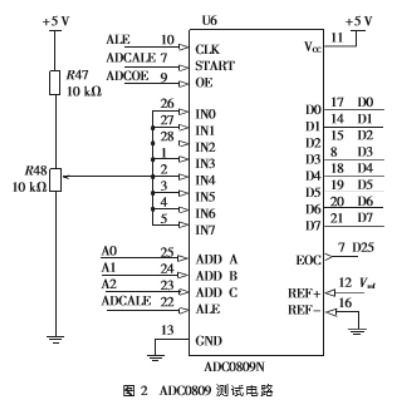

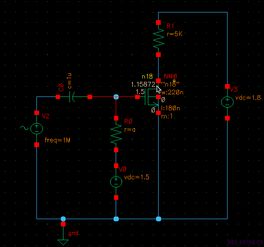

- 時鐘與高速信號設計:時鐘信號通常是芯片中頻率最高、邊沿最陡的信號,是最大的潛在干擾源。設計時,時鐘樹的綜合、布線(是否采用差分對、屏蔽層)、緩沖器插入策略,都會影響其諧波輻射。同樣,高速數據總線(如DDR、SerDes)的拓撲、端接匹配、等長控制若不恰當,會產生信號完整性(SI)問題,如過沖、振鈴和串擾,這些都會轉化為電磁輻射。

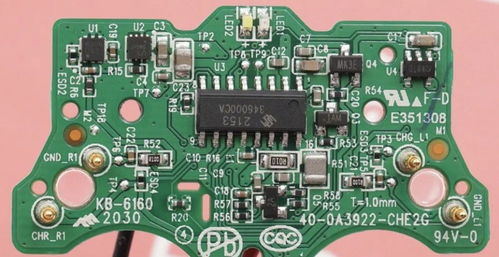

- 輸入/輸出(I/O)單元與封裝:I/O驅動器是芯片與外部世界的接口,其驅動強度、壓擺率控制、同時開關噪聲(SSN)管理至關重要。過強的驅動或過快的邊沿會產生豐富的諧波。封裝的選擇(如引線鍵合與倒裝焊)、封裝內的電源/地引腳分配、寄生電感電容,都會極大地影響芯片引腳處的噪聲和輻射效率。這些必須在芯片-封裝協同設計時就進行優化。

- 襯底耦合與內部噪聲:在深亞微米工藝下,晶體管密度極高,通過公共硅襯底的噪聲耦合(襯底噪聲)成為一個嚴重問題。數字電路的開關噪聲會通過襯底干擾敏感的模擬電路(如RF模塊、PLL、ADC),導致性能下降。這需要通過設計合理的隔離結構(如深N阱、保護環)和物理布局隔離來緩解。

- 設計方法與工具:現代IC設計離不開EDA工具。在設計階段利用EMC/SI分析工具進行預仿真,如電源完整性(PI)分析、信號完整性(SI)分析、以及近場輻射仿真,可以在流片前識別潛在熱點。諸如“設計即正確”的方法學,強調通過設計規則檢查(DRC)、電氣規則檢查(ERC)以及特定的EMC設計規則來規避問題。

因此,“90%的EMC問題是設計出來的”并非夸張。它強調的是一種預防性的哲學:與其在后期測試中耗費巨資進行整改和迭代,不如在成本投入最低、靈活性最高的設計初期,就系統性地將EMC作為一項核心設計約束。對于集成電路設計師而言,這意味著需要具備跨領域的知識,將系統級EMC要求轉化為芯片級的物理和電氣設計決策。

結論是,一顆EMC性能優良的芯片,必定是“精心設計出來”的。它從架構規劃、電路實現、物理布局到封裝選擇,每一個環節都融入了對電磁能量的控制與管理。這正是EDA365等平臺和社區強調設計重要性、推廣先進設計方法與工具的意義所在——賦能設計師在源頭扼殺EMC問題,打造出真正可靠、高性能的集成電路產品。